RVAM16基于RISC-V和ARMthumb的低成本多ISA处理器

嵌入式领域不断增长的需求导致了几种令人印象深刻的指令集架构(ISA)的出现。然而,当处理器从一种ISA迁移到另一种ISA时,软件兼容性问题是不可避免的。

尽管可以使用软件二进制翻译系统来确保软件兼容性,但这些系统在低成本嵌入式系统中具有局限性(例如性能和功率)。

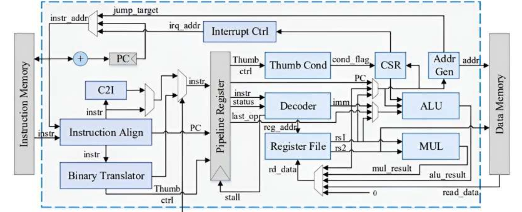

针对嵌入式领域最流行的两种ISARISC-V和ARMThumb,黄立波教授领导的研究团队提出了基于硬件二进制翻译的多ISA处理器RVAM16作为解决软件兼容性的解决方案。多ISA处理器不仅避免了软件DBT系统的启动和额外运行时间,而且可以直接执行所有非本地ISA程序,从而不会遭受SBT的困境。

通过针对RISC-V流水线中ARMThumb条件标志、分支指令和条件执行指令的硬件优化技术,RVAM16显着缩小了在基于HBT的多ISA处理器中运行本机ISA程序和非本机ISA程序之间的性能差距。此外,为了将RVAM16的面积和功耗保持在可接受的范围内,研究团队使用分时复用16位数据路径技术设计了32位处理器。

该研究还实现并评估了同时支持RV32IMC和ARMv6-M的RVAM16原型处理器。评估结果显示,在运行非原生ARMThumb程序时,与单独使用硬件二进制翻译相比,RVAM16实现了超过2.73倍的显着加速,达到原生RISC-V程序性能的70%以上。另一方面,与具有类似功能的传统单ISA处理器相比,RVAM16在面积和功耗方面也具有可比性。

此外,通过对二进制转换器和相关硬件优化单元进行适当的调整,可以有效地利用所提出的架构来适应任何一对不同的ISA。

这种灵活性使RVAM16微架构成为一种引人注目的多功能解决方案,可解决来自不同ISA的软件兼容性挑战。

免责声明:本答案或内容为用户上传,不代表本网观点。其原创性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本站不作任何保证或承诺,请读者仅作参考,并请自行核实相关内容。 如遇侵权请及时联系本站删除。